I. M. Dharmadasa

# Advances in THIN-FILM SOLAR CELLS

## Advances in THIN-FILM SOLAR CELLS

This page intentionally left blank

I. M. Dharmadasa

## Advances in THIN-FILM SOLAR CELLS

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2012 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Version Date: 20120829

International Standard Book Number-13: 978-9-81436-412-6 (eBook - PDF)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www. copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

### Contents

| Pr  | reface  | 2       |                                               | xiii |

|-----|---------|---------|-----------------------------------------------|------|

| Lis | st of S | Symbols | s and Abbreviations Used in the Book          | xvii |

|     |         | _       |                                               | _    |

| 1   |         |         | aic Solar Energy Conversion                   | 1    |

|     | 1.1     |         | luction                                       | 1    |

|     |         |         | voltaic Effect                                | 2    |

|     |         |         | Energy Materials                              | 3    |

|     | 1.4     | Electr  | onic Devices Used for Solar Energy Conversion | 4    |

|     |         | 1.4.1   | p-n Junctions                                 | 5    |

|     |         | 1.4.2   | p-i-n Junctions                               | 6    |

|     |         | 1.4.3   | Hetero-Junctions                              | 7    |

|     |         |         | n-n and p-p Junctions                         | 8    |

|     |         | 1.4.5   | Metal/Semiconductor (or Schottky) Contacts    | 8    |

|     |         | 1.4.6   | Metal-Insulator–Semiconductor Interfaces      | 11   |

|     | 1.5     | Chara   | cteristics of a Solar Cell                    | 13   |

|     |         | 1.5.1   | I-V Characteristics of a Solar Cell Under     |      |

|     |         |         | Dark Conditions                               | 13   |

|     |         | 1.5.2   | I-V Characteristics of a Solar Cell Under     |      |

|     |         |         | Illuminated Conditions                        | 16   |

|     |         | 1.5.3   | How to Maximise $V_{\rm oc}$                  | 19   |

|     |         | 1.5.4   | How to Maximise $J_{sc}$                      | 20   |

|     |         | 1.5.5   | How to Maximise FF                            | 20   |

|     | 1.6     | Next-   | Generation Solar Cells                        | 21   |

|     | 1.7     | Summ    | hary                                          | 22   |

| 2   | Stat    | us Rep  | oort on Solar Energy Technologies             | 25   |

|     | 2.1     | Introd  | luction                                       | 25   |

|     | 2.2     | Si Sola | ar Cell Technology                            | 27   |

|     | 2.3     | PV-Ma   | anufacturing Cost Based on Si Technology      | 30   |

|     | 2.4     | PV Te   | chnology Based on III-V Compounds             | 31   |

|   | 2.5        | New Technology for PV and Nano-Divices                 | 32 |

|---|------------|--------------------------------------------------------|----|

|   | 2.6        | Emerging Low-Cost Thin-Film Technologies               | 33 |

|   | 2.7        | Summary                                                | 35 |

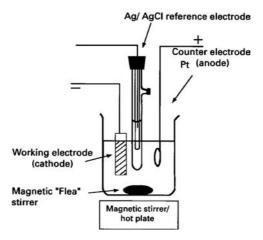

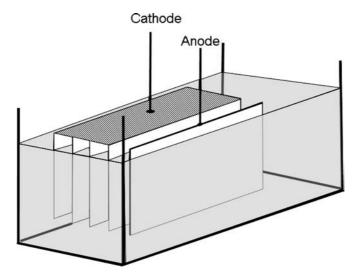

| 3 | Ele        | ctrochemical Deposition of Solar Energy Materials      | 37 |

|   | 3.1        | Introduction                                           | 37 |

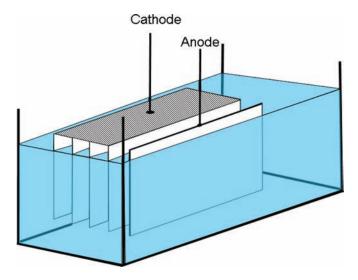

|   | 3.2        | Electrodeposition of Semiconductors                    | 38 |

|   | 3.3        | 0 1                                                    | 40 |

|   |            | 3.3.1 Simplicity, Low-Cost, Scalability, and           |    |

|   |            | Manufacturability                                      | 40 |

|   |            | 3.3.2 Self-Purification and Built-in Hydrogen          |    |

|   |            | Passivation                                            | 41 |

|   |            | 3.3.3 Extrinsic and Intrinsic Doping                   | 42 |

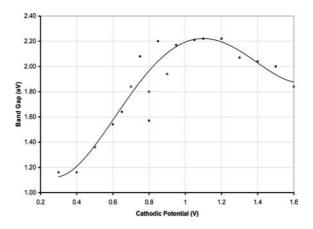

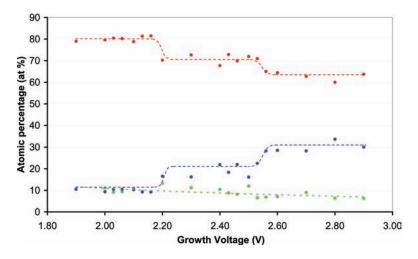

|   |            | 3.3.4 Ability in Bandgap Engineering                   | 43 |

|   |            | 3.3.5 Other Advantages of Electrodeposition            | 43 |

|   | 3.4        | I · · · · · · · · · · · · · · · · · · ·                | 44 |

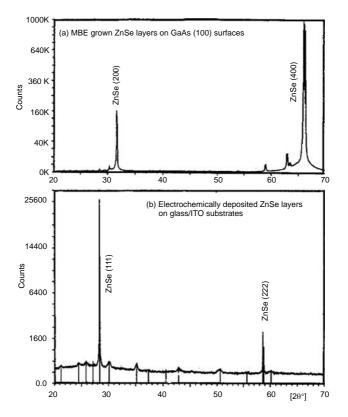

|   |            | 3.4.1 Observations in XRD                              | 44 |

|   |            | 3.4.2 Observations in XRF                              | 44 |

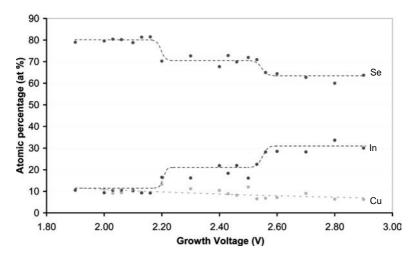

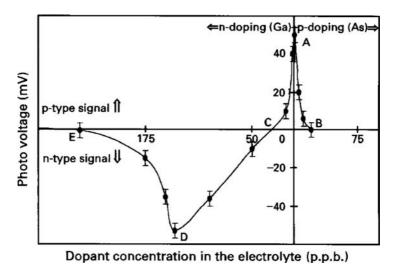

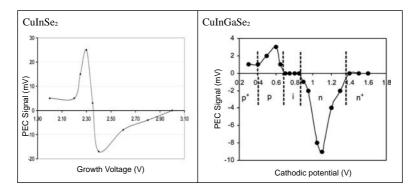

|   |            | 3.4.3 Observations in PEC Cell Measurements            | 46 |

|   |            | 3.4.4 Observations in Optical Absorption               |    |

|   |            | Measurements                                           | 49 |

|   |            | 3.4.5 Observations in Photoluminescence                | 49 |

|   | - <b>-</b> | 3.4.6 Impurity Control in Semiconductors               | 51 |

|   | 3.5        | I I I I I I I I I I I I I I I I I I I                  | 51 |

|   | 3.6        |                                                        | 53 |

|   | 3.7        | Summary                                                | 56 |

| 4 | Bac        | kground of the CdTe Solar Cell and                     |    |

|   |            | New Device Concept                                     | 59 |

|   | 4.1        | Introduction                                           | 59 |

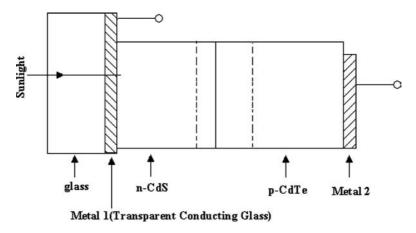

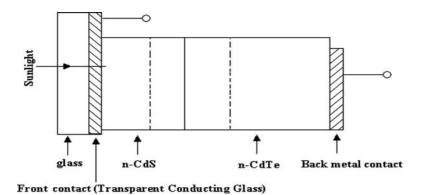

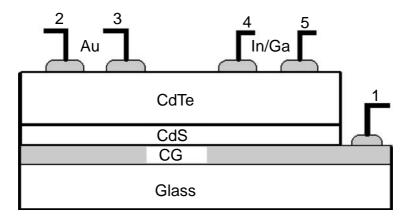

|   | 4.2        |                                                        |    |

|   |            | Glass/CdS/CdTe/Metal Solar Cell                        | 60 |

|   | 4.3        | Key Observations That Led to the Formulation of        |    |

|   |            | a New Model                                            | 63 |

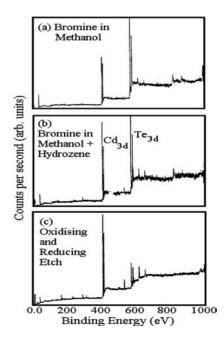

|   |            | 4.3.1 Surface Modification of CdTe                     | 63 |

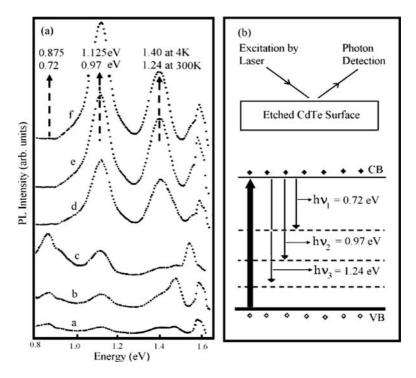

|   |            | 4.3.2 Effects of Surface Modification on Defect Levels |    |

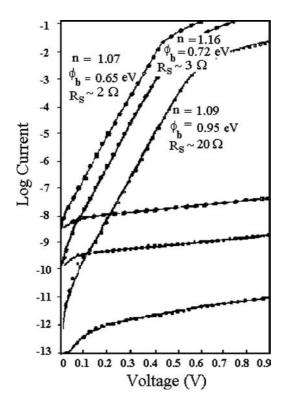

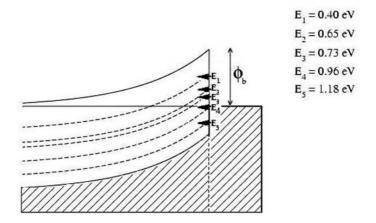

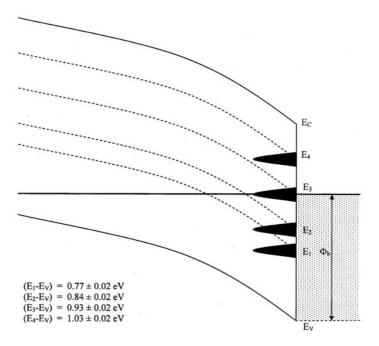

|   |            | 4.3.3 Effects of Defect Levels on Electronic Devices   | 65 |

|   |            | 4.3.4              | Similar Observations on Thin-Film CdS/CdTe     |                 |

|---|------------|--------------------|------------------------------------------------|-----------------|

|   |            |                    | Solar Cells                                    | 66              |

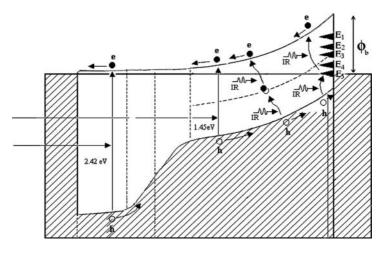

|   | 4.4        | New (              | Concept for CdS/CdTe Solar Cell                | 68              |

|   | 4.5        | Descr              | iption of Experimental Results Using the       |                 |

|   |            | Two I              | Models                                         | 71              |

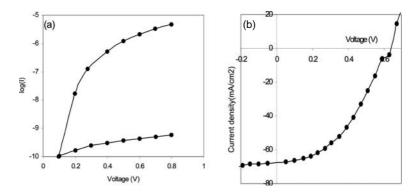

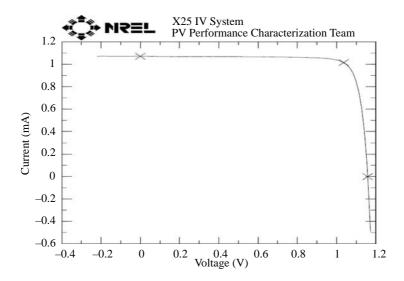

|   |            | 4.5.1              | Current-Voltage (I-V) Characteristics          | 72              |

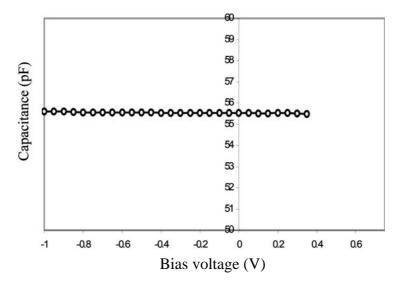

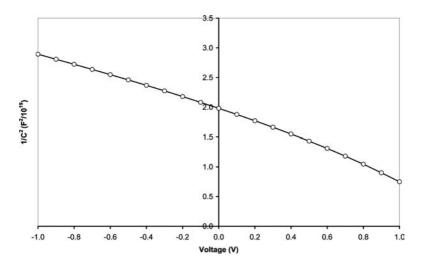

|   |            | 4.5.2              | Capacitance-Voltage (C-V) Characteristics      | 73              |

|   |            | 4.5.3              | Electron Beam–Induced Current                  |                 |

|   |            |                    | Measurements                                   | 73              |

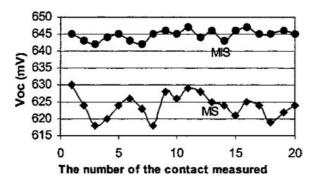

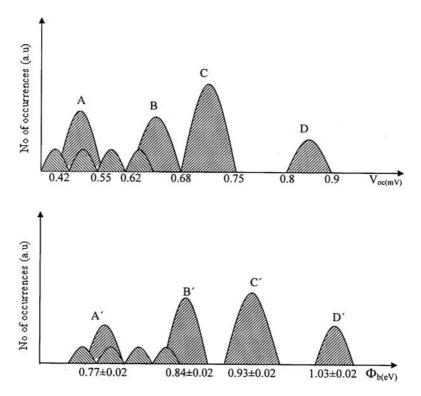

|   |            | 4.5.4              | Observation of Discrete Barrier Heights and    |                 |

|   |            |                    | V <sub>oc</sub> Values                         | 74              |

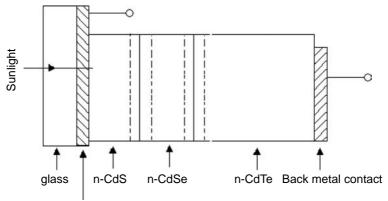

|   |            | 4.5.5              | A Thin-Film CdTe Solar Cell Device Without     |                 |

|   |            |                    | a CdS Layer                                    | 74              |

|   |            | 4.5.6              | Results From Electrical Contacting Work        | 75              |

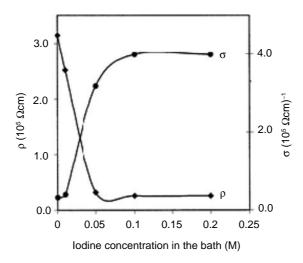

|   |            | 4.5.7              | Doping of CdS and CdTe Layers                  | 76              |

|   |            | 4.5.8              | Further Experimental Evidence to Confirm       |                 |

|   |            |                    | the True Structure of the Device               | 78              |

|   | 4.6        | Predi              | ctions for Further Development of CdS/CdTe     |                 |

|   |            | Solar              | Cells and Latest Observations                  | 80              |

|   |            | 4.6.1              | Doping of Window and Absorber Materials        |                 |

|   |            |                    | with n-Dopants                                 | 80              |

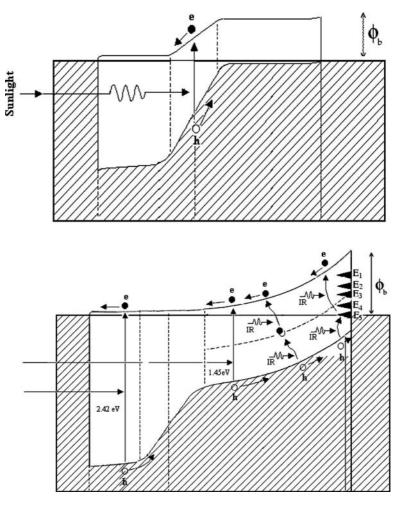

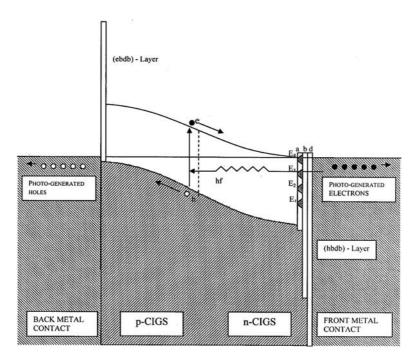

|   |            | 4.6.2              | Improvements to Back Contact Using MIS-Type    |                 |

|   |            |                    | Structures                                     | 86              |

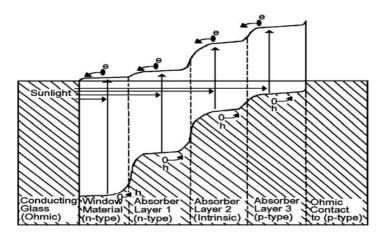

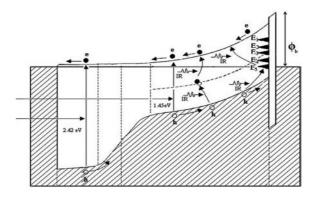

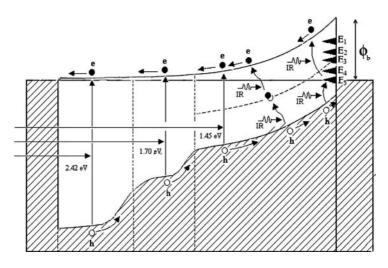

|   |            | 4.6.3              | A Multi-Layer Graded Bandgap Approach          | 88              |

|   |            | 4.6.4              | Dealing with Defects                           | 89              |

|   | 4.7        | Sumn               | nary                                           | 91              |

| _ | Б.         |                    |                                                |                 |

| 5 |            | ension<br>ar Cells | of the New Model to CIGS Thin-Film             | 95              |

|   |            |                    |                                                | <b>95</b><br>95 |

|   |            |                    | duction                                        | 95              |

|   | 5.2        | Mater              | nary of Accumulated Knowledge on CIGS-Based    | 00              |

|   |            |                    |                                                | 96              |

|   |            | 5.2.1              | Different Growth Techniques                    | 96              |

|   |            | 5.2.2              | Structural, Optical, and Electronic Properties | 96              |

|   |            | 5.2.3              | 1 5                                            | 97              |

|   | <b>-</b> 2 |                    | Latest Developments in Materials Growth        | 97              |

|   | 5.3        |                    | nary of Accumulated Knowledge on CIGS-Based    | 00              |

|   |            | Solar              | Lelis                                          | 98              |

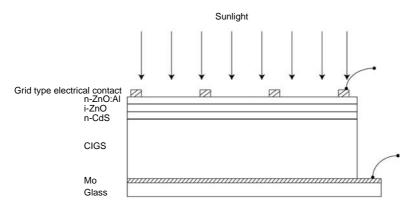

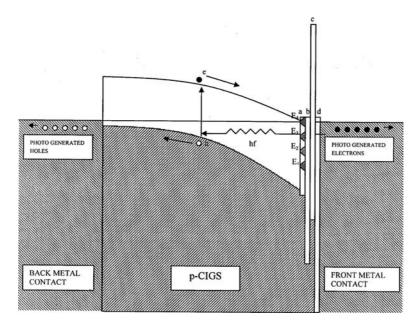

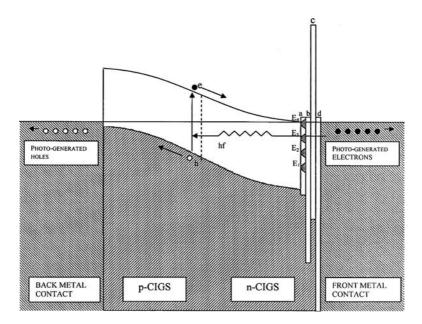

|   |      | 5.3.1   | Conventional Device Structure                   | 98  |

|---|------|---------|-------------------------------------------------|-----|

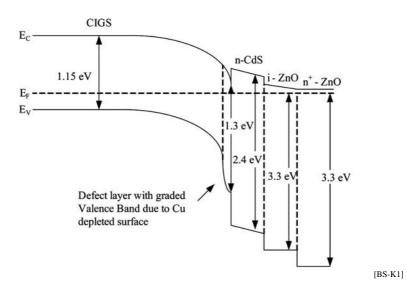

|   |      | 5.3.2   | Frequently Used Energy Band Diagram             | 99  |

|   | 5.4  | Curre   | nt Views of the Physics Behind CIGS Solar Cells | 100 |

|   |      | 5.4.1   | p-CIGS/n-CdS Hetero-Junction                    | 101 |

|   |      | 5.4.2   | p-CIGS/n-CIGS Homo-Junction                     | 101 |

|   |      | 5.4.3   | p-CIGS/n-ODC Hetero-Junction                    | 101 |

|   | 5.5  | Repor   | rted Device Performance                         | 102 |

|   | 5.6  | Recen   | it Work on Metal/p-CIGS Interfaces              | 104 |

|   | 5.7  | Deepe   | er Understanding of Mo/CIGS/CdS/i-ZnO/          |     |

|   |      | n-ZnC   | Al/Metal-Grid Solar Cells                       | 106 |

|   |      | 5.7.1   | Type-I CIGS-Based Solar Cell                    | 106 |

|   |      | 5.7.2   | Type-II CIGS-Based Solar Cell                   | 109 |

|   | 5.8  | Discu   | ssion on Further Improvements of CIGS           |     |

|   |      | Solar   | Cells                                           | 112 |

|   |      | 5.8.1   | Optimisation of Growth, Doping, and             |     |

|   |      |         | Bandgap Engineering                             | 112 |

|   |      | 5.8.2   | Defect Level Identification and Engineering     | 113 |

|   |      | 5.8.3   | Growth of CIGS with Controlled Orientation      | 113 |

|   |      | 5.8.4   | Replacement of Mo Using TCO for Tandem          |     |

|   |      |         | and Double-Faced Solar Cells                    | 114 |

|   |      | 5.8.5   | Further Improvements of the Device Structure    | 114 |

|   | 5.9  | Concl   | usions                                          | 115 |

|   | 5.10 | ) Sumn  | nary                                            | 117 |

| 6 | Effe | ctive H | Iarvesting of Photons                           | 123 |

|   | 6.1  | Introd  | luction                                         | 123 |

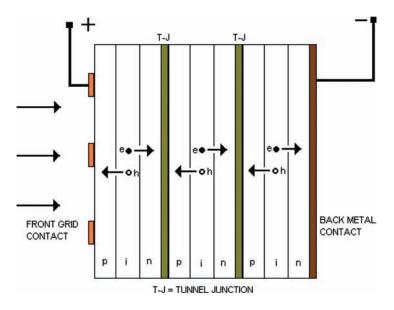

|   | 6.2  | Tande   | em Solar Cells                                  | 123 |

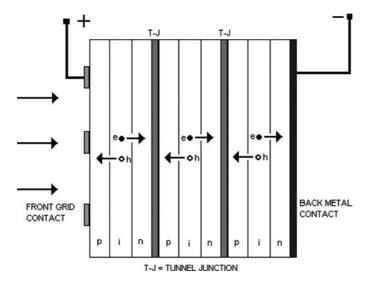

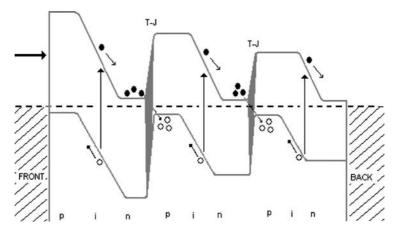

|   |      | 6.2.1   | Connection in Series                            | 124 |

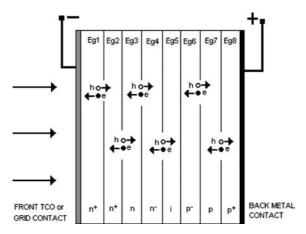

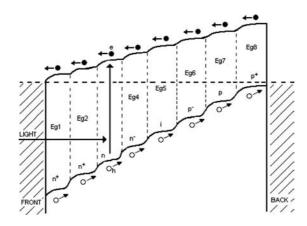

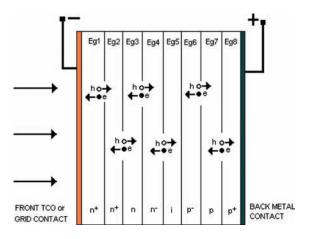

|   |      | 6.2.2   | Connection in Parallel                          | 125 |

|   | 6.3  | Comp    | arison of the Two Connecting Methods            | 127 |

|   |      | 6.3.1   | Disadvantages of Series Connections             | 128 |

|   |      | 6.3.2   | Advantages of Parallel Connections              | 129 |

|   | 6.4  | Concl   | usions                                          | 131 |

|   | 6.5  | Sumn    | lary                                            | 132 |

| 7 | Mul  | ti-Laye | er Graded Bandgap Solar Cells                   | 135 |

|   | 7.1  | Introd  | duction                                         | 135 |

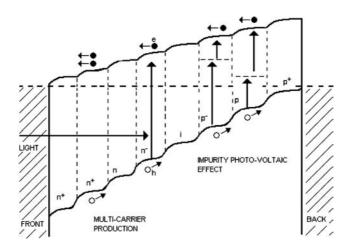

|   |      | 7.1.1   | Incorporation of Impurity PV Effect             | 136 |

|   |      | 7.1.2 Incorporation of Impact Ionisation               | 137 |

|---|------|--------------------------------------------------------|-----|

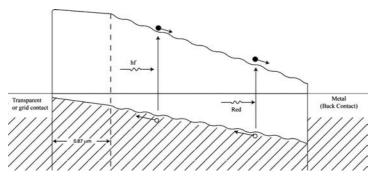

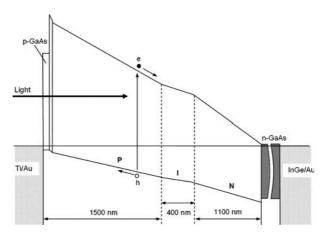

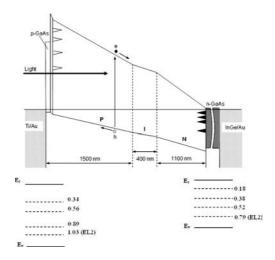

|   | 7.2  | Summary of Growth and Process Details of               |     |

|   |      | the Device Structure                                   | 137 |

|   | 7.3  | Experimental Results of Fully Processed                |     |

|   |      | Devices                                                | 138 |

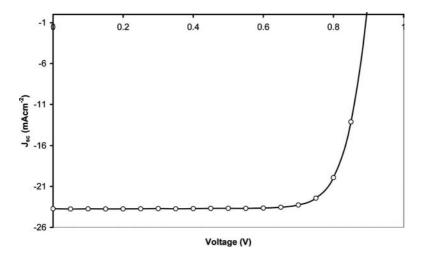

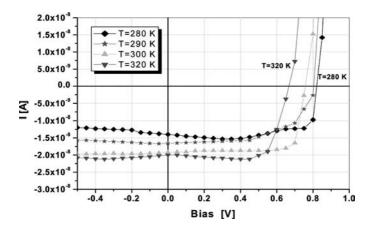

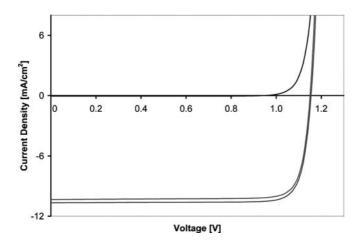

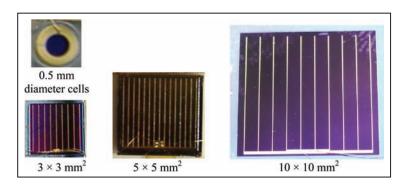

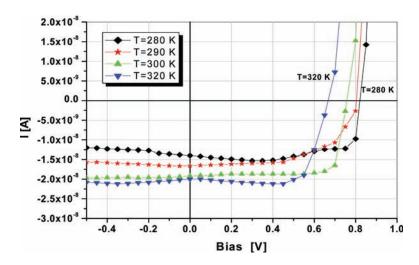

|   |      | 7.3.1 Electrical Properties Under Dark Conditions      | 139 |

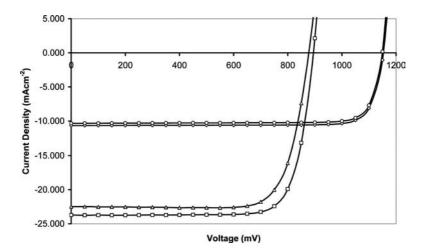

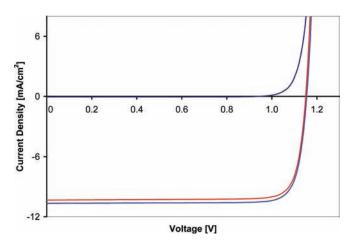

|   |      | 7.3.2 Electrical Properties Under AM1.5 Illumination   | 141 |

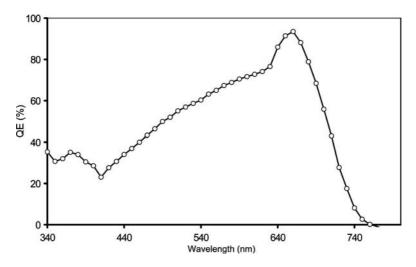

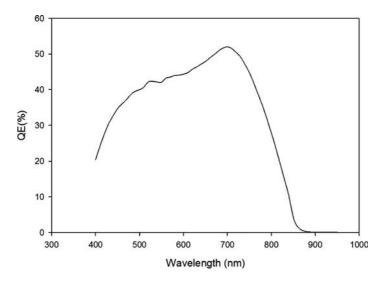

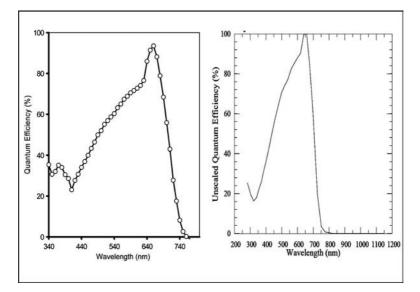

|   |      | 7.3.3 IPCE Measurements                                | 143 |

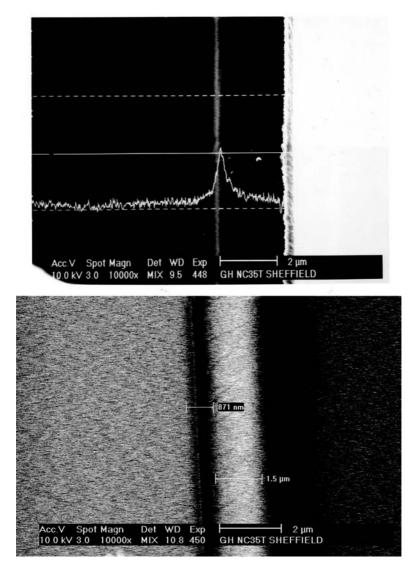

|   |      | 7.3.4 EBIC Measurements                                | 143 |

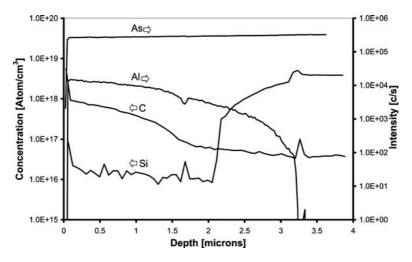

|   |      | 7.3.5 SIMS Profiling                                   | 144 |

|   |      | 7.3.6 Optimisation of Si Doping Concentration          | 147 |

|   | 7.4  | Discussions                                            | 151 |

|   | 7.5  | Summary                                                | 153 |

| 8 | Sola | ar Cells Active in Complete Darkness                   | 155 |

|   | 8.1  | Introduction                                           | 155 |

|   | 8.2  | Summary of Experimental Results                        | 155 |

|   | 8.3  | Search for Experimental Evidence of the Impurity       |     |

|   |      | PV Effect                                              | 156 |

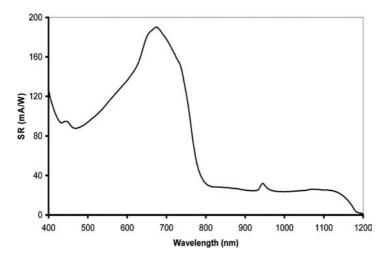

|   | 8.4  | Responsivity Measurements                              | 158 |

|   | 8.5  | I-V Measurements Under Dark Conditions                 | 158 |

|   |      | 8.5.1 I-V as a Function of Light Intensity             | 159 |

|   |      | 8.5.2 I-V Measurements Under Complete Darkness         | 160 |

|   | 8.6  | Discussion                                             | 162 |

|   | 8.7  | Conclusions                                            | 164 |

|   | 8.8  | Summary                                                | 164 |

| 9 | Effe | cts of Defects on Photovoltaic Solar Cell              |     |

|   | Cha  | racteristics                                           | 167 |

|   | 9.1  | Introduction                                           | 167 |

|   | 9.2  | Variations of I-V Characteristics of Metal/n-CdTe      |     |

|   |      | Interfaces                                             | 168 |

|   | 9.3  | Effects on the Performance of CdS/CdTe Solar Cells     | 171 |

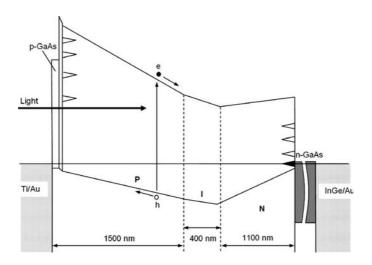

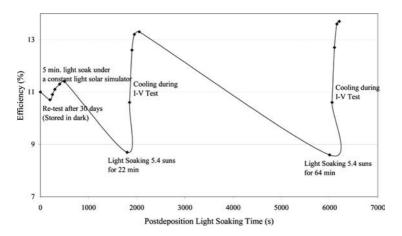

|   | 9.4  | Variations in GaAs/AlGaAs Solar Cells                  | 173 |

|   |      | 9.4.1 Device Structures Used                           | 173 |

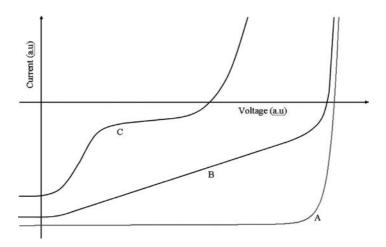

|   |      | 9.4.2 Instability of I-V Characteristics               | 175 |

|   |      | 9.4.3 Application of Electrical Stresses to the Device | 175 |

|   |      | 9.4.4 Discussion and Possible Explanations             | 177 |

|   |      |                                                        |     |

**x** Contents

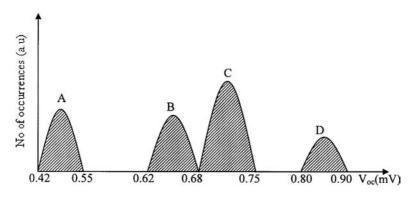

|    | 9.5   | Variations in CIGS Solar Cells                      | 183 |

|----|-------|-----------------------------------------------------|-----|

|    | 9.6   | Summary                                             | 185 |

| 10 | A Fu  | ture Dominated by Solar Energy                      | 189 |

|    | 10.   | 1 Introduction                                      | 189 |

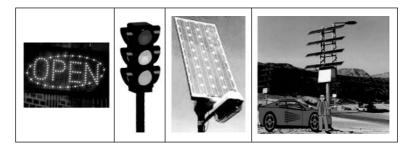

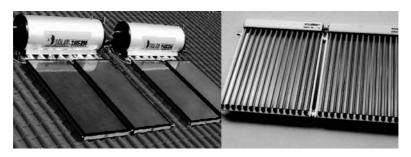

|    | 10    | 2 Early Applications with Low Power Requirements    | 190 |

|    | 10    | 3 Early Applications with Moderate Power            |     |

|    |       | Requirements                                        | 190 |

|    | 10    | 4 Applications in Solar Home Systems                |     |

|    |       | ( $\sim$ 50 W Range)                                | 191 |

|    | 10    | 5 Applications in Drip Irrigation Systems           |     |

|    |       | ( $\sim$ 100 W Range)                               | 193 |

|    | 10    | 6 Applications in Powering Computers                |     |

|    |       | (500–1,000 W Range)                                 | 194 |

|    | 10    | 7 Applications in Large-Scale Water Pumping         |     |

|    |       | ( $\sim$ 1,000 W and Above)                         | 195 |

|    | 10    | 8 Solar Power Applications on Roads                 | 198 |

|    | 10    | 9 Solar Power Applications on Buildings             |     |

|    |       | ( $\sim$ 3 kW and Above)                            | 199 |

|    | 10.1  | 0 Energy from Solar Farms and Deserts               |     |

|    |       | (MW Range)                                          | 202 |

|    | 10.1  | 1 Recommendations for Developing Countries          | 203 |

|    | 10.1  | 2 Recommendations for Developed Countries           | 204 |

|    | 10.1  | 3 Summary                                           | 205 |

| 11 | Is Fe | ermi-Level Pinning Affecting GaAs-Based             |     |

|    | Sola  | r Cells?                                            | 207 |

|    | 11.1  | Introduction                                        | 207 |

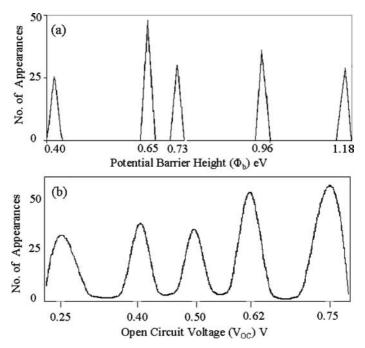

|    |       | Observation of Discrete Sets of I-V Characteristics | 207 |

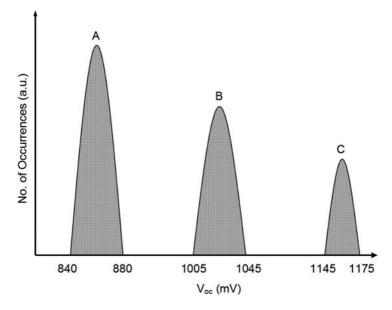

|    |       | Observation of Discrete Sets of $V_{\rm oc}$ Values | 208 |

|    | 11.4  | Discussion of New Observations                      | 209 |

| 12 | Tho   | ughts on Future Directions of Thin-Film Solar       |     |

|    |       | Research and Development                            | 211 |

|    | 12.1  | -                                                   | 211 |

|    | 12.2  | Areas for Research and Development Efforts          | 211 |

|    |       | 12.2.1 Dealing with Defects in Thin-Film Device     |     |

|    |       | Structures                                          | 211 |

|    |       |                                                     |     |

|       | 12.2.2 | Is impact Ionisation Contributing to the       |     |

|-------|--------|------------------------------------------------|-----|

|       |        | PV Effect?                                     | 212 |

|       | 12.2.3 | Are Intermittent Observations of High $J_{sc}$ |     |

|       |        | Values Genuine?                                | 212 |

|       | 12.2.4 | Graded Bandgap Multi-Layer Structures          |     |

|       |        | for Next-Generation Solar Cells                | 214 |

| 12.3  | Conclu | sions                                          | 215 |

| Index |        |                                                | 217 |

This page intentionally left blank

#### Preface

Sunlight was first converted into electricity by Edmund Becquerel in 1839, but until the 1950s, no considerable development had taken place. However, during the two decades of the 1950s and the 1960s, Si-based solar cells were developed, manufactured, and used in applications such as satellites and remote communication stations. The first oil crisis, in the early 1970s, gave a huge push to the search for alternative energy conversion methods, and researchers actively searched for new materials and low-cost device structures. As a result, thin-film solar cells based on III-V compounds (GaAs and InP), amorphous Si, CdTe, and CuInGaSe<sub>2</sub> (CIGS) were introduced to mainstream solar energy conversion. In the early 1990s, dve-sensitised solar cells were introduced, and organic solar cells came in the early 2000s. With the renewed interest in nanomaterials, researchers worldwide are exploring the ways of using new materials in solar cell devices. At present, all these photovoltaic (PV) fronts are moving toward producing low-cost and high-efficiency solar cells to convert sunlight into electricity.

The main hurdle in the rapid market penetration of solar energy applications is their high cost. Although there are active research programmes to reduce manufacturing costs and increase conversion efficiencies, the progress is painfully slow for various reasons—one reason being the lack of deeper understanding of material issues and physics behind solar cell devices. This book does not deal with well-documented semiconductor properties and device principles but presents the latest developments and advances in thin-film solar cells, with an introduction to the most required background knowledge. The targeted audience will be undergraduate and postgraduate students in science and engineering; electronic device researchers in chemistry, material science, physics, mathematics, and engineering; and PV module developers and technologists in the industry. This book concentrates mainly on advances in thin-film solar cells based on CdTe-, CIGS-, and GaAs-based devices, but the ideas are equally applicable to all thin-film solar cells.

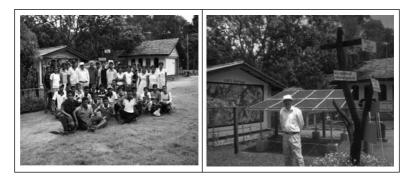

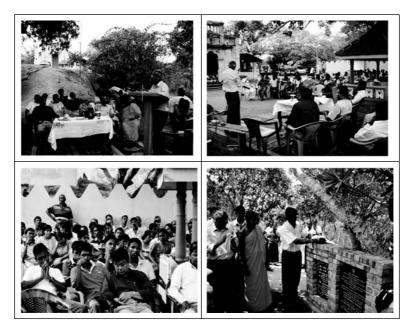

Chapter 1 of this book introduces solar energy conversion to all readers in a simple manner with the aid of diagrams, references, and animations placed on the author's website. The next chapter provides a brief status report on PV technology. The main barrier in the PV sector is the high manufacturing cost due to the use of expensive materials (Si and III-V compounds) and the high energy consumption during materials growth and device processing. The initial high capital cost of equipment also exacerbates this situation. As a solution to this, a low-cost and scalable materials growth technique (electro-chemical deposition) for II-VI and alloy compounds will be described in chapter 3. This growth method is also a suitable low-cost technique for growing nanomaterials for various other applications in nanotechnology. In all solar cells, two electrical contacts are needed to extract the photo-generated charge carriers from the device and, hence, these metal/semiconductor (MS) interfaces play a very important role in the overall performance. Chapter 4 summarises the most striking recent breakthroughs which improved the understanding of PV action in thin-film solar cells. This chapter describes the history of the CdTe solar cell, the application of new ideas to this device, the formation of a new concept to describe the solar energy conversion process, and the way forward for the development of the device. Chapter 5 extends the applicability of the Fermi-level pinning concept to CIGS-based solar cells. The next three chapters are devoted to revisiting the current practice in tandem solar cells based on tunnel junctions and the use of multi-layer graded bandgap device structures in solar energy conversion. The latter device design has been experimentally tested with a well-researched GaAs/AlGaAs system. This device has shown highest reported open circuit voltage of 1175 mV with the highest achievable fill factor of  $\sim$ 0.86 for a single device. The new device concept is mainly based on a set of defects within these devices, and chapter 9 describes the effects of defects on the performance of solar cells. It also describes the way forward for dealing with defects in order to achieve higher performance in devices. Chapter 10 is for the general public and describes the scenario of a future dominated by solar energy. This is based on author's two decades of public understanding of science activities and real projects carried out on the ground. The solar village project designed and piloted successfully by the author is described, and the replication plans are indicated in this chapter. There are two short chapters included at the end of this book chapter 11 presents the evidence collated to date for Fermi-level pinning in GaAs-based solar cells, and chapter 12 indicates some thoughts on future directions of thin-film solar cell research.

I am grateful to all the people who have supported me to develop and progress in this sector. My PhD supervisors, late Sir Professor Gareth Roberts and Professor Mike Petty at Durham University, put me on the right track at the very beginning, in the late 1970s. Working with active scientists in the field. Professors R. H. Williams and E. H. Rhoderick, enabled me to be well established in this field during my four-year postdoctoral research in University College Cardiff, in early 1980s. Since then, I have worked on and learned the subject from numerous colleagues from chemistry, physics, mathematics, and engineering disciplines, both in academia and in the industry (BP Research, Sunbury). During the last two decades of my academic career at Sheffield Hallam University, many postdoctoral researchers, 14 PhD students, and numerous visiting researchers contributed to this work in order to understand the chemistry and physics behind these complex materials and devices. University lecturing on relevant subjects like electricity and magnetism, thermodynamics, solid-state physics, quantum mechanics, high-specification materials, device design and manufacture, and Si processing in clean room environment for over three decades helped me in understanding these complex devices. This accumulated knowledge, new breakthroughs, and recent advances are presented in this book to share with the present and future scientists, engineers, and the general public. I am grateful to my immediate family for their help and support during this journey. In particular, I thank Dahiru Diso, Osama Elsherif, Ajith Weerasinghe, Obi Kingsley Echendu, Fijay Bin Fauzi, Tamara Dharmadasa, Ruvini Dharmadasa, and Asela Dharmadasa for their contributions during the preparation of this book. I also thank Sidath Kalyanaratne and Nishith Patel for preparing some of the diagrams used in this book.

Finally, this book is dedicated to my beloved parents, who worked hard to support me during my childhood with limited resources while living in a sun-rich environment in Sri Lanka. I am hopeful that this book will contribute to reverse this situation for future generations by bringing prosperity to all the people who live wherever the sun is shining.

#### I. M. Dharmadasa

Professor and Head of Electronic Materials & Sensors Group Materials & Engineering Research Institute Sheffield Hallam University, United Kingdom March 2012

### List of Symbols and Abbreviations Used in the Book

| ,                     |                                               |

|-----------------------|-----------------------------------------------|

| h                     | Planck constant                               |

| f                     | frequency in Hz                               |

| e                     | electronic charge                             |

| k                     | Boltzmann constant                            |

| χ                     | electron affinity                             |

| $\varepsilon_0$       | dielectric permittivity of free space         |

| $\varepsilon_{\rm s}$ | dielectric permittivity of semiconductor      |

| ε <sub>r</sub>        | relative permittivity of semiconductor        |

| σ                     | electrical conductivity                       |

| Т                     | temperature in Kelvin                         |

| $\phi_{ m b}$         | potential barrier height                      |

| $\phi_{ m m}$         | metal work function                           |

| Eg                    | energy bandgap of a semiconductor             |

| $A^*$                 | Richardson constant for thermionic emission   |

| S                     | area of a solar cell                          |

| n                     | ideality factor of a diode                    |

| $V_{\rm oc}$          | open circuit voltage of solar cells           |

| I <sub>sc</sub>       | short circuit current of solar cells          |

| J <sub>sc</sub>       | short circuit current density of solar cells  |

| FF                    | fill factor, or curve factor, of solar cells  |

| η                     | solar to electric power conversion efficiency |

| CdTe                  | cadmium telluride                             |

| CIGS                  | copper indium gallium diselenide              |

| GaAs                  | gallium arsenide                              |

| AlAs                  | aluminium arsenide                            |

| 11113                 | aranimum al seniue                            |

This page intentionally left blank

#### **Chapter 1**

#### **Photovoltaic Solar Energy Conversion**

#### 1.1 Introduction

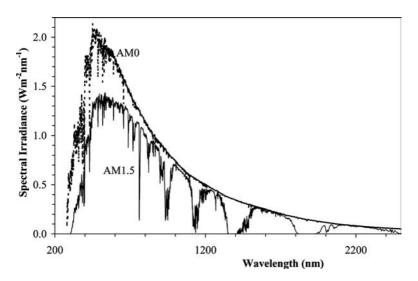

Sunlight consists of electromagnetic radiation in the regions of ultraviolet (UV), visible light, and infrared (IR) radiation. The solar spectrum reaching the earth's surface undergoes various absorptions in the air atmosphere, and the average solar energy falling on the earth's surface is generally known as air-mass 1.5 (AM1.5) irradiation, which is equal to approximately  $100 \text{ mW cm}^{-2}$ . This quantity is equal to  $\sim 1.0$  kW of power falling on every square metre, which humankind has not yet effectively utilised. The shape of the solar spectrum and the absorption of various wavelengths under AM1.5 conditions are shown in Fig. 1.1. Traditionally, there are two ways of capturing solar energy. One method is to absorb mainly the heat energy (or IR radiation), and this is generally known as 'solar thermal technology'. The second method is to convert UV and visible light (photons) directly into electricity (measured in volts). Since the photons are directly converted into volts, this method is known as 'photovoltaic conversion' (PV conversion for short). This book concentrates only on the second method, which is PV conversion.

Advances in Thin-Film Solar Cells

I. M. Dharmadasa

Copyright © 2013 Pan Stanford Publishing Pte. Ltd.

ISBN 978-981-4316-07-1 (Hardcover), 978-981-4364-12-6 (eBook)

www.panstanford.com

2 Photovoltaic Solar Energy Conversion

Figure 1.1 The approximate shape of the solar spectrum under AM1.5 condition. The shape of the spectrum before entering the air atmosphere (AM0 condition) is also shown for comparison [1].

#### 1.2 Photovoltaic Effect

In the process of effective PV energy conversion, four basic steps must be brought together simultaneously. These are:

- (a) Absorption of photons using a suitable material

- (b) Creation of charge carriers (electron-hole, or e-h pairs) mainly by breaking bonds between atoms

- (c) Separation of oppositely charged free carriers before their recombination

- (d) Collection or transportation of photo-generated charge carriers through electrical contacts and their passage through an external circuit to create useful electric current.

If any of these four processes is hindered or not taking place, the device will show poor conversion efficiency, or zero PV activity. Bringing these four stages together by selecting the right materials and putting them together in a suitable device structure is a challenging task. In PV research, this task is twofold — (i) exploring

new materials with the right properties to absorb light and create charge carriers effectively and (ii) fabricating suitable devices to separate and transport charge carriers out of the device and through an external circuit.

#### 1.3 Solar Energy Materials

All materials around us can be classified into three main groups: electrical conductors, semiconductors, and insulators. This classification can be done according to the electrical conductivity ( $\sigma$ ) or the energy bandgap ( $E_g$ ) of the materials. Table 1.1 summarises the two main properties of these different classes of materials, but it should be noted that there is no clear demarcation among these classes. For more details and specific properties of different materials, the reader is requested to refer to already published books in materials [2–4], solid-state physics [5–7], and solid-state chemistry [8–9].

The materials used for the absorption of light and creation of charge carriers come from semiconductor families. Over the past 70 years, scientists have identified many different semiconducting materials with a wide variety of properties. Table 1.2 displays some relevant elements from the Periodic Table, and Table 1.3 shows many different semiconductors available today. The task for the PV community is to identify the most suitable semiconductors to effectively absorb light and create charge carriers for solar energy conversion. High optical absorption, a direct instead of indirect bandgap, and low density of recombination centres, together with required mechanical strengths and stability, are some of the desired properties for solar energy materials. In addition, these materials should have the required qualities to make appropriate electronic devices in order to separate and collect photo-generated charge carriers. When these materials are prepared in the form of thin films

Table 1.1 A summary of two main properties of different classes of electronic materials

| Parameter                                                | Electrical Conductors         | Semiconductors          | Electrical Insulators       |

|----------------------------------------------------------|-------------------------------|-------------------------|-----------------------------|

| $\sigma \ (\Omega \ \mathrm{cm})^{-1} \equiv \mathrm{S}$ | $\sim 10^8$ – $10^1$          | $\sim 10^1$ – $10^{-8}$ | $\sim 10^{-8}$ - $10^{-20}$ |

| $E_{\rm g}$ (eV)                                         | $\sim$ 0.3 or negative values | $\sim$ 0.3–4.0          | $\sim$ 4.0–10.0             |

with thicknesses of a few microns, the situation becomes even more complex due to the effects of surface states.

| Group I | Group II | Group III | Group IV | Group V | Group VI |

|---------|----------|-----------|----------|---------|----------|

| Cu      | Zn       | В         | С        | N       | S        |

| Ag      | Cd       | Al        | Si       | Р       | Se       |

|         |          | Ga        | Ge       | As      | Те       |

|         |          | In        | Sn       | Sb      | 0        |

Table 1.2 The most common elements used for the production of semiconductors, with their groups assigned in the Periodic Table

Table 1.3 A summary of semiconductor material families available for use in PV devices

| Semiconductor Family               | Examples of Semiconductors                         |

|------------------------------------|----------------------------------------------------|

| Elemental semiconductors           | C, Si, Ge                                          |

| III-V semiconductors               | AlN, AlP, AlAs, AlSb                               |

|                                    | GaN, GaP, GaAs, GaSb                               |

|                                    | InN, InP, InAs, InSb                               |

| II-VI semiconductors               | ZnS, ZnSe, ZnTe, ZnO                               |

|                                    | CdS, CdSe, CdTe, CdO                               |

| Ternary compound semiconductors    | $CuInSe_2(CIS)$ , $Cd_xMn_{(1-x)}Te$ ,             |

|                                    | $Cd_xHg_{(1-x)}$ Te, $Al_xGa_{(1-x)}As$            |

| Quaternary compound semiconductors | CuInGaSe <sub>2</sub> (CIGS), AgInGaSSe, CuZnSnSSe |

#### 1.4 Electronic Devices Used for Solar Energy Conversion

Once the suitable solar energy materials are selected, the optimum growth conditions have been established, and the materials are fully characterised for their mechanical, structural, optical and electrical properties, the next task is to design and fabricate an effective electronic device capable of creating and separating photogenerated charge carriers before they recombine. This requires a strong built-in electric field within the electronic device. The heart of a PV device is, therefore, one or more interfaces created by combining suitable semiconductors and two electrical contacts to extract charge carriers from these devices. Therefore, in a typical PV device, several interfaces can be incorporated, made out of electrical conductors, semiconductors, and insulators. The following sections examine different basic interfaces used in electronic device structures. Several of these basic interfaces can then be combined to form an efficient PV solar cell.

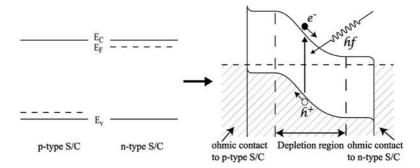

#### 1.4.1 p-n Junctions

The most basic interface is the p-n junction formed within one semiconductor crystal lattice having p-type and n-type electrical conduction in two adjacent regions. These types of junctions are generally known as homo-junctions, and the energy band diagram is shown in Fig. 1.2. The slope produced in the energy band diagram represents the built-in electric field (E = -dV/dX) available within the device. The region here with this band bending (or the area with the built-in electric field) is known as the 'depletion region', and this region is the heart of this basic electronic device. The basic properties of p-type and n-type semiconductors are summarised in Table 1.4 for quick reference, but readers are advised to refer to a suitable textbook for further information on fundamental materials and device properties [10–12].

When photons with energy (hf) greater than the bandgap of the semiconductor  $(hf \ge E_g)$  fall in the depletion region, photons are absorbed and bonds between the atoms are broken to create free e-h pairs. The existing internal electric field separates these photo-generated charge carriers due to their opposite charges,

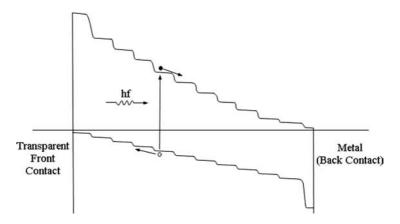

**Figure 1.2** The energy band diagram of a p-n homo-junction and the mechanism of PV activity within a solar cell based on a p-n junction.

| p-Type Semiconductors                         | n-Type Semiconductors                                       |  |

|-----------------------------------------------|-------------------------------------------------------------|--|

| • The majority charge carriers are holes.     | • The majority charge carriers are electrons.               |  |

| • The minority charge carriers are electrons. | <ul> <li>The minority charge carriers are holes.</li> </ul> |  |

| These semiconductors are doped                | These semiconductors are doped with                         |  |

| with externally added acceptors, native       | externally added donors, native defects,                    |  |

| defects, or variation in composition.         | or variation in composition.                                |  |

| The Fermi level is positioned close to the    | • The Fermi level is positioned close to the                |  |

| valence band.                                 | conduction band.                                            |  |

Table 1.4 A summary of main properties of p-type and n-type semiconductors

forcing them in opposite directions, towards the two electrical contacts on both sides of the junction. If the built-in electric field is weak or non-existent, photo-generated charge carriers will recombine again and the photo-current will be low or zero. Therefore, the key to improving the PV activity is to fabricate a healthy depletion region, with a strong built-in electric field, using a semiconductor with high optical absorption properties and low recombination centres.

The action of a solar cell based on a p-n junction is demonstrated by animation on Dharme's blog at: www.apsl.org.uk to help beginners in this field visualise the PV process.

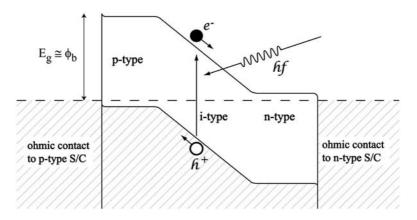

#### 1.4.2 p-i-n Junctions

The production of a healthy depletion region depends on the doping concentration of the two semiconductor regions used to fabricate the p-n junction. Low doping concentrations produce a wide depletion region, and heavy doping concentrations create a thin depletion layer, which are not helpful for PV conversion. Optimising the doping concentration to create a depletion region width comparable to the thickness of a thin film solar cell, typically in the order of 2  $\mu$ m, to achieve the best performance is a real challenge faced by material scientists and device physicists during the research and development phase. The exact value of the depletion region width depends on the device design planned for a particular purpose.

**Figure 1.3** The energy band diagram of a p-i-n diode and the mechanisms of PV activity within the device.

One improvement generally used is the fabrication of p-i-ntype interfaces. The energy band diagram of a p-i-n device is shown in Fig. 1.3, and an intrinsic (or insulating) semiconductor is sandwiched between p- and n-type semiconducting layers.

This arrangement aligns the Fermi levels of the two semiconductors through the intrinsic layer to create a strong internal electric field throughout the i-layer and hence control the width of the depletion region for a specific application. This is also a reliable method to form a high potential barrier approaching the bandgap of the semiconducting material used ( $E_g \approx \phi_b$ ). Animation to illustrate the formation and use of a p-i-n diode as a solar cell is presented in Dharme's blog at www.apsl.org.uk. This will be helpful in understanding electron transfer during junction formation, bandbending process, and visualisation of the PV actions of the p-i-n-type solar cell device.

#### 1.4.3 Hetero-Junctions

A hetero-junction is another simple modification of the p-n-type interface. Instead of one semiconducting material on both sides of a homo-junction, two different semiconductors are used to form the interface (Fig. 1.4). The main difference is the existence of two different energy bandgaps on either side. An advantage of

**Figure 1.4** The energy band diagram of a hetero-junction diode with two ohmic contacts on both sides. Energy bandgaps on two sides are different, and interface states have been introduced.

using two different semiconductors in the device is the absorption of different regions of the solar spectrum. However, in heterojunctions, one semiconductor needs to be physically grown on another semiconductor, which can introduce detrimental surface states (or defects) affecting the performance of the device due to crystal lattice mismatch, the existence of surface states, and foreign atoms such as carbon and oxygen.

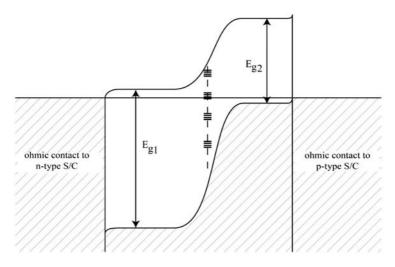

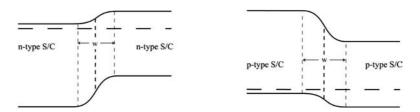

#### 1.4.4 n-n and p-p Junctions

Interfaces with internal electric fields can also be created using only one type of semiconductor, by combining materials having different energy bandgaps as shown in Fig. 1.5. Although the potential step created at each interface is small in this case, these can be joined together to form graded bandgap multi-layer solar cells, as described in detail in section 1.6 and later in this book.

#### 1.4.5 Metal/Semiconductor (or Schottky) Contacts

A solar cell device with one or more interfaces creating its depletion region, and hence the built-in electric field, requires

**Figure 1.5** Hetero-junction interfaces from n-n and p-p junctions creating small steps of potential barriers.

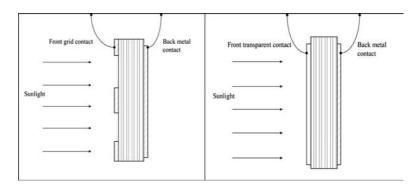

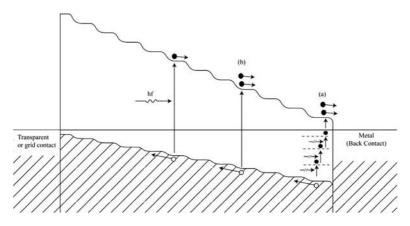

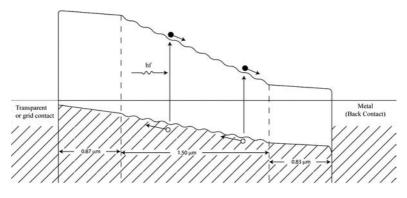

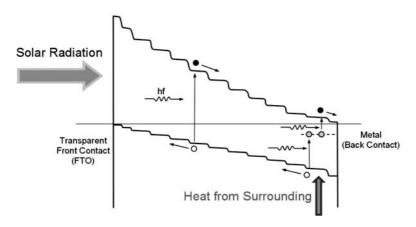

**Figure 1.6** Solar cells based on a grid type or transparent front contact providing the conditions required for PV solar cells.

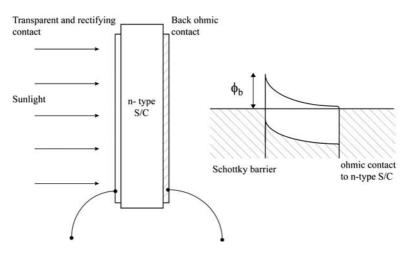

two electrical contacts on either side to effectively collect the photo-generated charge carriers and transport them through an external circuit. These electrical contacts are usually formed using metal/semiconductor (MS), or Schottky, contacts. The front electrical contact should either take the form of a grid contact to minimise the effect of shading or be transparent to incoming light (Fig. 1.6). Depending on the design of the solar cell device, the MS interface could have either ohmic or rectifying properties. For comprehensive information on MS interfaces, readers can refer to textbooks written on this particular subject [13, 14].

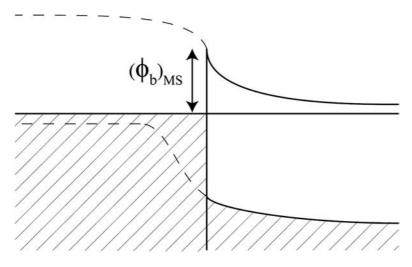

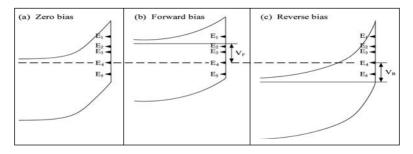

As a brief summary of Schottky barrier formation, Fig. 1.7 presents the energy band diagram of a metal/n-type semiconductor interface. When a metal having a work function  $\phi_m$  is brought into intimate contact with an n-type semiconductor having an electron affinity  $\chi$ , a potential barrier height ( $\phi_b$ ) is formed at the interface. If there are no surface states or other defects arising from the material,

**Figure 1.7** Schottky barrier formation at a metal/n-type semiconductor when an ideal interface is formed between the two materials.

the  $\phi_{\rm b}$  formed at this interface is given by:

$$\phi_{\rm b} = \phi_{\rm m} - \chi \tag{1.1}$$

The formation of potential barriers at the metal/p-type semiconductor is very similar, but the band bending will be in the opposite direction, forming potential barriers for the flow of holes. The above description is valid only for ideal interfaces, but the situation is very different for interfaces strongly affected by semiconductor defects, surface or interface states. In these situations, the Fermi level will be pinned by the defect states and hence  $\phi_{\rm b}$  is independent of the metal used for the formation of the electrical contact. The drastic effects of Fermi-level pinning will be discussed in detail in later chapters of this book.

The nature of the potential barrier formed at the MS interface will govern the electrical properties of this interface. If the  $\phi_b$  is in excess of ~0.40 eV and the width of the depletion region (*W*) is considerable, the interface will have rectifying electrical properties described by Eq. 1.2 [13, 14].

$$I_{\rm D} = SA^*T^2 \cdot \exp\left(\frac{-e\phi_{\rm b}}{kT}\right) \left[\exp\left(\frac{eV}{nkT}\right) - 1\right]$$

(1.2)

where  $I_D$  = Electric current in dark condition S = Area of the contact  $A^*$  = Richardson constant for thermionic emission T = Temperature in Kelvin

e = Electronic charge $\phi_{\rm h} = \text{Potential barrier height}$ k = Boltzmann constantn = Ideality factor of the diode

These types of potential barriers are formed when the semiconductor has moderate doping concentration of  ${\sim}10^{15}\text{--}10^{17}~\text{cm}^{-3}.$  When the  $\phi_{\rm b}$  is less than ~0.40 eV — or the depletion region is narrow - the electrical conduction through the interface will exhibit linear (ohmic) behaviour due to the ease of electron transfer in both directions. Heavy doping, in excess of  $10^{18}$  cm<sup>-3</sup>, will form a thin enough depletion layer, enabling charge carriers to tunnel through the interface showing ohmic behaviour. Both rectifying and ohmic electrical contacts can be incorporated in PV solar cells in order to maximise the internal electric field present in these devices.

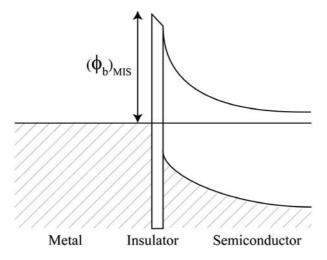

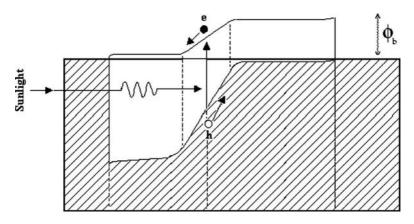

#### 1.4.6 Metal-Insulator–Semiconductor Interfaces

In general, the  $\phi_{\rm b}$  values obtained at MS interfaces are much smaller than those of p-n junctions for a given semiconductor. As indicated in Fig. 1.8, the Schottky barrier represents approximately half of a p-n junction and, hence, a lower  $\phi_{\rm h}$ .

This disadvantage can be removed by incorporating an insulating layer, as shown in Fig. 1.9. The suitably thin insulating layer decouples the metal from the semiconductor and increases the band bending or the potential barrier at the interface. The rectification property of this structure improves, and the interface behaviour is described by Eq. 1.3 [15]:

$$I_{\rm D} = SA^*T^2 \exp(-\chi^{1/2}\delta) \exp\left(\frac{-\phi_{\rm b}}{kT}\right) \exp\left(\frac{eV}{nkT}\right)$$

(1.3)

where  $\chi$ , in electron volts, is the mean barrier height presented by the interfacial layer of thickness,  $\delta$ , in Angströms (Å).

As described in section 1.5.3, the open circuit voltage ( $V_{oc}$ ) of a solar cell is a function of the  $\phi_{\rm b}$  and, therefore, this is a method used to enhance the  $V_{oc}$  of PV solar cells based on Schottky diodes. The insulating layer brings an additional advantage of minimising the interactions between the metal and the semiconductor. In the case

**Figure 1.8** A schematic diagram showing that a Schottky barrier is only a half of a p-n junction in the case of an ideal interface.

**Figure 1.9** The enhancement of the  $\phi_b$  and the decoupling of two materials by the incorporation of an insulating layer at the interface.

of an organic insulator, this layer prevents the in- and out-diffusion of metal and semiconductor elements. This layer also prevents chemical reactions between the two inorganic materials, the metal and the semiconductor. This leads to an increase in the device lifetime, removing ageing effects at the electrical contact. This is an ideal way to improve performance, stability, and lifetime of PV solar cells by fabricating hybrid-devices combining inorganic and organic materials.

In the place of an insulating layer, a p-type conducting polymer can be used. In this case, the intermediate layer can have large thicknesses, which will be an advantage in producing organicinorganic hybrid devices.

#### 1.5 Characteristics of a Solar Cell

As described in the above sections, a typical PV cell contains one or more interfaces producing rectifying property and two electrical contacts on both sides to collect charge carriers. The nature of the two electrical contacts can vary according to the device design used, with generally used ohmic contacts. However, metal contacts with rectifying properties can also be used to enhance the existing electric field within the device, as described in later chapters of this book. The following section uses a simple solar cell device structure based on a rectifying Schottky diode to illustrate the characteristics of a solar cell and its conversion efficiency. Details of other PV solar cell devices are well documented in previous publications [16–20].

#### 1.5.1 *I-V Characteristics of a Solar Cell Under Dark Conditions*

Figure 1.10 shows a schematic diagram and the corresponding energy band diagram of a simple solar cell based on a rectifying Schottky contact formed on an n-type semiconductor. The front contact can be fabricated using a transparent electrical contact or grid type contact to minimise the effect of shading. The back electrical contact is a usual ohmic contact to collect charge carriers.

**Figure 1.10** A schematic diagram of a PV solar cell based on a rectifying Schottky contact and an ohmic back contact formed on an n-type semiconductor, together with its energy band diagram.

The current-voltage (I-V) characteristics of a Schottky diode under dark conditions can be expressed by Eq. 1.2 [13, 14]:

$$I_{\rm D} = SA^*T^2 \cdot \exp\left(\frac{-e\phi_{\rm b}}{kT}\right) \left[\exp\left(\frac{eV}{nkT}\right) - 1\right]$$

(1.2)

or

$$I_{\rm D} = I_0 \left[ \exp\left(\frac{eV}{nkT}\right) - 1 \right]$$

(1.4)

where  $I_0$  represents the saturation current.

For externally applied voltages across the diode above  ${\sim}75$  mV (V  ${\geq}~75$  mV):

$$\exp\left(\frac{eV}{nkT}\right) \gg 1 \tag{1.5}$$

Therefore, Eq. 1.4 can be simplified to the following form:

$$I_{\rm D} = I_0 \cdot \exp\left(\frac{eV}{nkT}\right) \tag{1.6}$$

The rearrangement of this equation provides a useful relation to analyse the I-V data measured under dark conditions for a PV device.

$$\log_{10}(I) = \left(\frac{e}{2.303nkT}\right) \cdot V + \log_{10}(I_{\rm D})$$

(1.7)

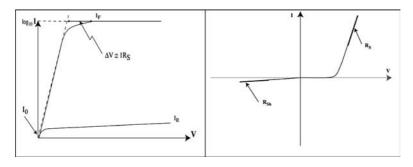

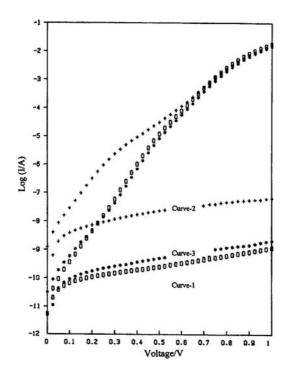

**Figure 1.11** The log-linear and linear-linear graphs plotted for detailed analysis of dark I-V characteristics of PV solar devices.

A plot of  $\log_{10}(I_D)$  versus the voltage applied (*V*) across the device takes the form of Fig. 1.11 for a practical device. It should be noted that both forward and reverse currents are plotted here in the same quadrant by changing the sign of the reverse voltages for convenience.

The rectification factor (RF) of the device, as defined by the expression RF = forward current/reverse current at a given voltage (say at V = 1.0 V) is a good indicator of the quality of rectifying diode. For an efficient solar cell, a large RF is desirable although an RF with a value of approximately  $10^3$  is sufficient.

The straight-line portion of the graph provides a value for the n from its gradient:

Gradient =

$$\left(\frac{e}{2.303nkT}\right)$$

(1.8)

This is a useful parameter as it provides a general idea about the current transport through the potential barrier [13]. For an ideal diode, the current transport takes place only through thermionic emission over the potential barrier and, hence, the *n* is equal to unity (n = 1.00). If the depletion region and the interface are full of recombination and generation (R&G) centres, the current transport is dominated by the R&G process and the value of the *n* becomes 2.00. In practical devices, both these transport mechanisms take place in parallel and, therefore, *n* takes values between 1.00 and 2.00. The situation becomes even more complicated when there is a large series resistance ( $R_s$ ) present in the device structure. The

value of  $R_s$  can be approximately evaluated using the potential drop at the high forward end of the I-V curve using Eq. 1.9:

$$\Delta V = I \cdot R_{\rm s} \tag{1.9}$$

Large values of  $R_s$  tend to reduce the gradient of the log-linear curve at the high forward-bias region and, hence, increase the *n*. Tunnelling through the device can also tend to increase the low forward bias current, decreasing the gradient of the log-linear I-V curve and, hence, increasing the *n*. When both effects are present in one device, the log-linear curve deviates accordingly, making the analysis more complicated. It should be noted that the largest gradient of this curve should be used to evaluate the smallest value of *n* and other parameters for accurate analysis of the device.

The intercept of the straight line with the highest gradient provides a more accurate value for  $I_0$ , and hence the  $\phi_b$  present in the device can be evaluated from:

$$I_0 = SA^*T^2 \cdot \exp\left(\frac{-e\phi_{\rm b}}{kT}\right) \tag{1.10}$$

This is a key parameter for a rectifying diode, and the production of an interface with a large  $\phi_b$  is desirable for making an efficient PV cell. In addition, the depletion region and the interface should have minimum amounts of R&G centres to produce a high-quality PV cell, minimising the detrimental leakage process through the barrier.

By plotting I-V data measured under dark conditions, in a linearlinear graph (as in Fig. 1.11), series resistance ( $R_s$ ) and shunt resistance ( $R_{sh}$ ) can also be estimated from the forward and reverse current portions respectively. Therefore, the dark I-V measurements provide the most important parameters (n,  $\phi_b$ ,  $R_s$ , and  $R_{sh}$ ) for the device structure and provide the quality of the depletion region and the information on current transport mechanisms in the device via the parameter n.

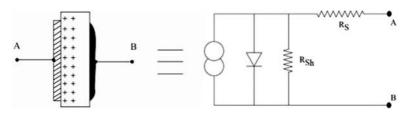

These parameters then help in establishing an equivalent circuit for the solar cell device, as shown in Fig. 1.12.

#### 1.5.2 *I-V Characteristics of a Solar Cell Under Illuminated Conditions*

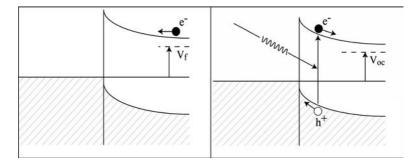

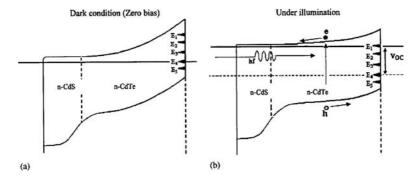

The directions of electron flow under dark and illuminated conditions are shown in the band diagrams in Fig. 1.13. This shows

**Figure 1.12** A schematic diagram of a Schottky barrier solar cell and its equivalent circuit.

that the photo-generated current flows in the opposite direction to the forward current under dark conditions. Therefore, the current through the diode under illumination is given by

$$I_{\rm L} = I_{\rm D} - I_{\rm sc} = I_0 \cdot \exp\left(\frac{eV}{nkT}\right) - I_{\rm sc}$$

(1.11)

where  $I_{sc}$  denotes the short circuit current produced by the solar cell under illumination.

**Figure 1.13** The direction of electron flow during forward bias under dark conditions and when used as a solar cell device under illuminated conditions.

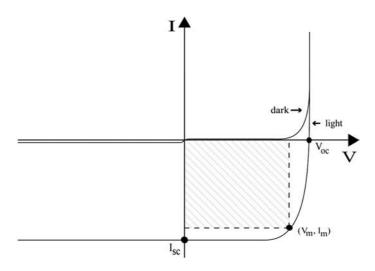

The I-V characteristics described by Eqs. 1.6 and 1.11 can then be plotted in a linear-linear graph, as shown in Fig. 1.14. There are four important parameters to consider for a solar cell device.

• Open circuit voltage ( $V_{oc}$ ): This is the voltage measured when the external circuit is in open condition, or when there is no current flow in the external circuit.

Figure 1.14 I-V characteristics of a PV solar cell under dark and illuminated conditions.

• Short circuit current density ( $J_{\rm sc}$ ): This is the current density produced when the two contacts are short circuited, or when there is zero voltage across the two contacts. This parameter is expressed as mAcm<sup>-2</sup> for convenience and provides easy comparison between devices fabricated with varying contact areas.

$$\left(J_{\rm sc} = \frac{I_{\rm sc}}{S}\right) \tag{1.12}$$

• Fill factor, or the curve factor (FF): This is a fraction defined to indicate the shape of the curve or the fraction of electric power that can be extracted from the solar cell. Therefore, the FF is defined as

$$FF = \frac{V_m I_m}{V_{oc} I_{sc}}$$

(1.13)

where  $V_{\rm m}$  and  $I_{\rm m}$  represent the parameters at the maximum power extraction point ( $V_{\rm m}$ ,  $I_{\rm m}$ ).

• Conversion efficiency  $(\eta)$ : After defining the above three parameters, the light to electric power conversion efficiency is defined as

$$\eta = \frac{\text{Output Power}}{\text{Input Power}} = \frac{V_{\text{m}}I_{\text{m}}}{P_{\text{in}}} = \frac{V_{\text{oc}} \cdot I_{\text{sc}} \cdot \text{FF}}{P_{\text{in}}}$$

(1.14)

when  $P_{in}$  is taken as the solar power incident on a unit area. The  $I_{sc}$  should be replaced by the current density ( $J_{sc}$ ), giving

$$\eta = \frac{V_{\rm oc} \cdot J_{\rm sc} \cdot FF}{P_{\rm in}} \tag{1.15}$$

The standard AM1.5 condition provides the value of  $P_{\rm in} = 100$  mWcm<sup>-2</sup> as the solar constant to evaluate the efficiency of the device.

#### 1.5.3 How to Maximise V<sub>oc</sub>

The open circuit voltage achievable from a given junction depends on the electronic properties of that interface. In order to obtain an expression for the  $V_{oc}$  of a Schottky barrier solar cell, the diode characteristics under illumination (Eq. 1.11) can be used:

$$I_{\rm L} = I_0 \cdot \exp\left(\frac{eV}{nkT}\right) - I_{\rm sc} \tag{1.11}$$

By definition,  $V = V_{oc}$  when  $I_L = 0$ , or the external circuit is kept open, or the current through the external circuit is zero. This gives

$$0 = I_0 \cdot \exp\left(\frac{eV_{\rm oc}}{nkT}\right) - I_{\rm sc}$$

or

$$SA^*T^2 \cdot \exp\left(\frac{-e\phi_{\rm b}}{kT}\right) \cdot \exp\left(\frac{eV_{\rm oc}}{nkT}\right) = I_{\rm sc}$$

The rearrangement of this equation provides

$$V_{\rm oc} = n \left[ \phi_{\rm b} + \frac{kT}{e} \cdot \ln \left( \frac{J_{\rm sc}}{A^* T^2} \right) \right]$$

(1.16)

This indicates that the magnitude of  $V_{\rm oc}$  depends on the value of the  $\phi_{\rm b}$ , present at the interface. Therefore, to achieve high values of  $V_{\rm oc}$ , large potential barriers are desirable.

It is also evident that the  $V_{oc}$  depends on the value of n, the ideality factor of the diode. The value of n for an ideal Schottky diode with current-transport dominated by thermionic emission [13] is equal to unity (n = 1.00). But with current-transport dominated by R&G, n value is equal to 2.00, indicating a helpful parameter to

improve  $V_{\rm oc}$ . But in real devices,  $J_{\rm sc}$  is drastically reduced and, hence,  $V_{\rm oc}$  decreases.

There is another factor which affects the value of *n* of a Schottky diode. In the case of metal-insulator-semiconductor (MIS)-type interfaces, the *n* value and  $\phi_{\rm b}$  increase as the insulating layer is incorporated and this effect helps in increasing the  $V_{\rm oc}$  of a solar cell device [15].

In addition, the temperature of the cell also affects the  $V_{\rm oc}$ . As the temperature decreases, the  $V_{\rm oc}$  value increases due to minimisation of the thermal agitation of charge carriers. Therefore, in order to increase the  $V_{\rm oc}$  of a Schottky barrier–based solar cell, improvement of the  $\phi_{\rm b}$  by the incorporation of an insulator, the reduction of the temperature of the cell, and the minimisation of the R&G process within the cell structure are desirable.

## 1.5.4 How to Maximise J<sub>sc</sub>

The short circuit current density depends on the number of photogenerated charge carriers and their separation and collection rates in the external circuit. This requires efficient photon absorption from almost all regions of the solar spectrum by the materials used, effective carrier generations, and the high quality of the depletion region formed and hence the strength of the built-in electric field created. To increase the photo-generated charge carriers, impurity PV effect and impact ionisation can be combined together. With the right device design, the impurity PV effect can be used to create e-h pairs using surrounding heat energy. These will be described later, in chapters 6, 7, and 8, and are demonstrated by the latest experimental results. In addition, the detrimental R&G process and any other leakage paths must be removed from the device structure. To maximise the value of  $J_{sc}$ , the series resistance of the complete device must be minimised.

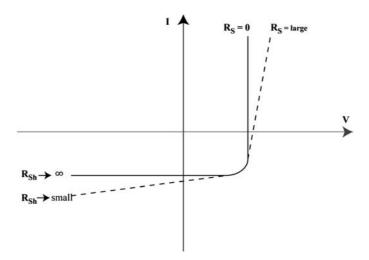

## 1.5.5 How to Maximise FF

To improve the shape of the I-V curve, and hence the FF, the total series resistance should be minimised (ideally  $R_s = 0$ ). This includes resistance introduced by the electrical contacts, interfaces within

**Figure 1.15** The effect of  $R_{\rm s}$  and  $R_{\rm sh}$  on I-V curves of PV solar cells.

the device, and materials used. The leakage resistance (or the shunt resistance) must be increased (ideally  $R_{\rm sh} \rightarrow \infty$ ). This can be achieved by minimising the R&G process and plugging any pinholes and other conducting paths in the material (Fig. 1.15).

#### 1.6 Next-Generation Solar Cells

Next-generation solar cells will be developed based on various systems. Some of these devices are based on organic materials, dyesensitised systems, and nanomaterials. However, the next stages of solar cells based on the most matured materials — inorganic semiconductors — have the highest potential to contribute towards solar energy conversion. This book, therefore, concentrates only on next-generation solar cells based on inorganic materials.

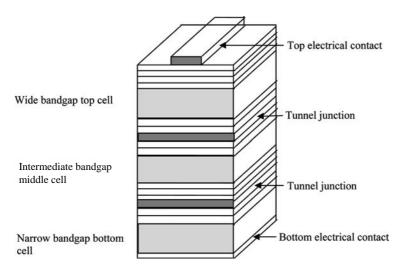

The basic interfaces used in solar cell devices are briefly described in this chapter. The next stage is to move forward and combine these basic interfaces to form more advanced PV devices. The aim is to effectively absorb the photons in almost all parts of the solar spectrum, create as many e-h pairs as possible, utilise other possible mechanisms such as impact ionisation and impurity

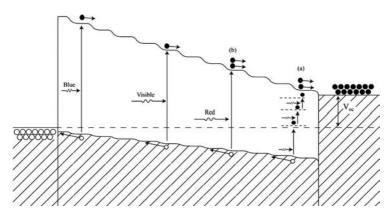

**Figure 1.16** Multi-layer graded bandgap solar cell structures possible on n-type and p-type window materials.

PV effect to increase charge carriers, minimise R&G mechanisms, and effectively separate and transport charge carriers through the external circuit. The best candidate to satisfy all these conditions is the graded bandgap multi-layer solar cell structure, as shown in Fig. 1.16, based on n-type and p-type window materials. Chapters 6, 7, and 8 are devoted to the discussion of these devices together with the latest experimental results to indicate their high potential.

It may be useful at this stage to note that the graded bandgap structures are based on a large number of p-p- or n-n-type heterojunctions and two ohmic contacts to the front and the back of the device. The front of the solar cell has wide bandgap n-type or ptype material, and the bandgap gradually decreases as it progresses towards the back of the solar cell. The electrical conduction type also gradually changes from n-type to p-type or p-type to n-type through the body of the device structure. The devices based on p-type window materials have potential barriers for electron transport, approximately equal to the bandgap of the wide bandgap window material, and hence the highest achievable  $\phi_{\rm b}$ . This means that the structures on p-type window materials are capable of achieving the highest possible  $V_{\rm oc}$  value since it is a function of the  $\phi_{\rm b}$ .

## 1.7 Summary

PV solar energy conversion consists of four main stages — (a) absorption of a major part of the solar spectrum, (b) effective

creation of charge carriers (e-h pairs) within the PV device, and (c) separation of (e-h) pairs before their recombination — in order to (d) pass through an external circuit to create useful power. To achieve these four functions simultaneously, an electronic device containing a suitable interface with a built-in electric field is necessary. Such an interface can be an MS Schottky contact, a p-n homo-junction, a p-n hetero-junction, an n-n hetero-junction, or a p-p hetero-junction. MS and p-n junctions can be further modified to form MIS and p-i-n junctions respectively to enhance their performance. To produce an efficient PV solar cell, two or more interfaces mentioned above can be combined to form one solar cell structure. The graded bandgap multi-layer solar cell structures are the way forward to improving solar energy conversion in the future.

## References

- 1. http://www.newport.com/store/genContent.aspx/Introduction-to-Solar Radiation/411919/1033.

- 2. R. Turton (2000) Physics of Solids, Oxford University Press.

- 3. D. H. Navon (1986) *Semiconductor Microdevices and Materials*, Holt, Rinehart and Winston.

- 4. J. N. Lalena and D. A. Clearly (2005) *Principles of Inorganic Materials Design*, John Wiley & Sons.

- 5. C. Kittel (2005) *Introduction to Solid State Physics*, 8th edn, John Wiley & Sons.

- 6. J. S. Blakemore (1974) *Solid State Physics*, 2nd edn, W. B. Saunders Company.

- 7. N. W. Ashcroft and N. D. Mermin (1976) *Solid State Physics*, Cengage Learning.

- 8. C. N. R. Rao and J. Gopalakrishnan (1997) *New Directions in Solid State Chemistry*, 2nd edn, Cambridge University Press.

- 9. L. E. Smart and E. A. Moore (2005) *Solid State Chemistry: An Introduction*, 3rd edn, Taylor & Francis Group.

- S. M. Sze and K. K. Ng (2007) *Physics of Semiconductor Devices*, John Wiley & Sons.

- 11. J. Singh (2001) Semiconductor Devices: Basic Principles, John Wiley & Sons.

- 12. S. O. Kasap (2001) *Optoelectronics and Photonics; Principles & Practices,* Prentice Hall.

- 13. E. H. Rhoderick and R. H. Williams (1988) *Metal-Semiconductor Contacts*, 2nd edn, Oxford Science Publications.

- 14. W. Mönch (2004) *Electronic Properties of Semiconductor Interfaces*, vol. 43, Springer Series in Surface Science.

- 15. G. G. Roberts, M. C. Petty, and I. M. Dharmadasa (1981) *IEE Proc.*, **128**(6), pp. 197–201.

- 16. T. Markvart (2000) Solar Electricity, 2nd edn, John Wiley & Sons.

- 17. J. Nelson (2003) The Physics of Solar Cells, Imperial College Press.

- 18. J. Poortmans and V. Arkhipov (eds) (2007) *Thin Film Solar Cells* (*Fabrication, Characterisation and Applications*), John Wiley & Sons.

- 19. J. A. Carson (ed.) (2008) *Solar Cell Research Progress*, Nova Science Publishers.

- 20. R. Scheer and Hans-Werner Schock (2012) *Chalcogenide photovoltaics*, Wiley-VCH.

## Chapter 2

# Status Report on Solar Energy Technologies

#### 2.1 Introduction

The energy radiated from the sun is equivalent to a million billion 100 GW power stations. Part of this energy reaches the planet Earth at a rate of  $\sim 1 \text{ kWm}^{-2}$ , but technology has succeeded in tapping only a tiny fraction of this energy to date. The sunlight falling on Earth consists of ultraviolet (UV), visible, and infrared (IR) (heat) radiation, and all renewable energy sources (hydro, wind, waves, biomass, etc.) arise due to the primary solar energy.

The PV effect was discovered by a French scientist, Edmund Becquerel, in 1839, when he was 19 years old. Edmund may have learned this subject area from watching his father, Cesar, known as the grandfather of electrochemistry, working with electrodes and electrolytes in his laboratory (Fig. 2.1).

Although the PV effect was discovered in 1839, considerable effort was not devoted to developing this until the 1950s. As an energy conversion method, the use of PV technology was not considered during the industrial revolution, with cheap coal and oil being available, and the future damage to the environment was not

Advances in Thin-Film Solar Cells

I. M. Dharmadasa

Copyright © 2013 Pan Stanford Publishing Pte. Ltd.

ISBN 978-981-4316-07-1 (Hardcover), 978-981-4364-12-6 (eBook)

www.panstanford.com

**Figure 2.1** The inventor of the PV effect, Edmond Becquerel was the second in four generations of a family of famous French physicists.

| Table 2.1 | A time line | of PV solar | energy technology |

|-----------|-------------|-------------|-------------------|

|-----------|-------------|-------------|-------------------|

| 1839:  | The PV effect was discovered by Edmund Becquerel when he was 19 years old.             |  |  |

|--------|----------------------------------------------------------------------------------------|--|--|

| 1883:  | The first solar cell using elemental Se as the light-absorbing material was developed. |  |  |

| 1916:  | Millikan provided experimental proof of the photoelectric effect.                      |  |  |

| 1918:  | Czochralski developed a method to grow single-crystal Si.                              |  |  |

| 1923:  | Albert Einstein won the Nobel Prize for explaining the photoelectric effect.           |  |  |

| 1954:  | 4.5% efficient Si solar cells were produced at Bell labs.                              |  |  |

| 1959:  | 10% efficient Si cells were produced, and the satellite Explorer-6 was                 |  |  |

|        | launched by the United States with a PV array of 9,600 cells.                          |  |  |

| 1960:  | 14% efficient Si solar cells were produced by Hoffman Electronics.                     |  |  |

| 1970s: | The first oil crisis kick-started the search for low-cost alternative systems          |  |  |

|        | for terrestrial energy conversion, accelerating PV research activities.                |  |  |

| 1980s: | Thin-film CdTe and CIGS solar cells were introduced into the mainstream of             |  |  |

|        | PV research.                                                                           |  |  |

| 1990s: | Dye-sensitised solar cell (DSSC) was introduced.                                       |  |  |

| 2000s: | Organic solar cells were introduced to the PV field.                                   |  |  |

envisaged at the time. But the relevant scientific research continued, and the main breakthroughs made are shown in Table 2.1 [1]. The first PV solar cell, with an efficiency of 4.5%, was produced in 1954 at Bell laboratories in the United States [2]. By 1960, 14% efficient Si solar cells were commercially produced and used in space applications. The first oil crisis, in 1970, kick-started the search for low-cost alternative methods for terrestrial energy conversion, and PV research was accelerated throughout the world.

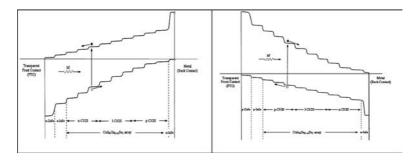

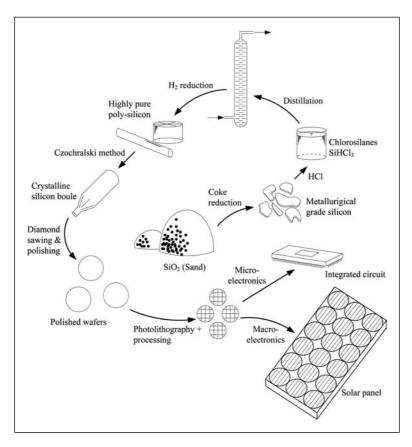

## 2.2 Si Solar Cell Technology

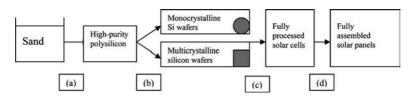

The fabrication of the interfaces required for PV devices, as described in chapter 1, needs a light-absorbing electronic material with the desired semiconducting properties. The most widely used material is Si, and it has undergone over 60 years of research and development. The main steps of growth of Si and device fabrication are given in Fig. 2.2. Si is produced starting with natural sand  $(SiO_2)$ , followed by four processing steps: (a) purification process, (b) crystallisation and wafer production, (c) processing of Si solar cells, and (d) assembly of the solar panels. This needs four different production lines, and these are summarised in Fig. 2.3 and Table 2.2. Each of these average-sized ( $\sim$ 25 MW) production lines could cost millions of dollars for the initial establishment. In addition, the whole process of converting sand into solar panels requires the heating of Si above its melting point (1,414°C), and repeated heating to high temperatures above 1,000°C, during solar cell fabrication. These steps demand a high energy input, burning fossil fuel, and therefore cost reduction is a challenging task for the Si PV industry.

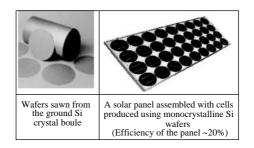

Figure 2.4 shows the main stages of the manufacturing process of solar panels based on crystalline Si: the growth of a monocrystalline cylindrical crystal boule using Czochralski method, grinding of the crystal boule in order to produce single-diameter Si wafers, and a fully assembled solar panel with crystalline Si wafers.

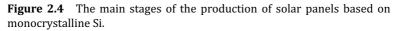

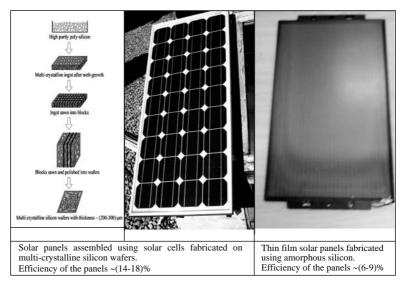

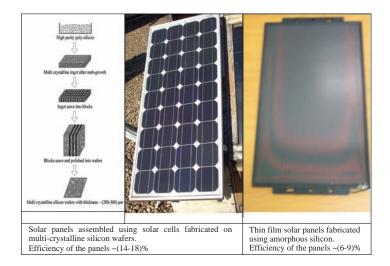

Figure 2.5 shows the main stages of the production process of multicrystalline Si solar panels and the appearance of thin-film solar panels manufactured with amorphous Si. By the appearance of the

**Figure 2.2** The main steps involved in the production of electronic-grade Si and device fabrication.

**Figure 2.3** The four industrial production lines required for the manufacturing of solar panels based on crystalline and polycrystalline Si.

| Production Line          | Input                                                 | Output                              |

|--------------------------|-------------------------------------------------------|-------------------------------------|

| (a) Si-purification line | Sand                                                  | High-purity polysilicon             |

| (b) Si-wafer line        | High-purity polysilicon                               | Mono- or multicrystalline Si wafers |

| (c) Si-cell line         | Mono- or multicrystalline Fully processed solar cells |                                     |

|                          | Si wafers                                             |                                     |

| (d) Si-module line       | Fully processed solar cells                           | Fully assembled solar panels        |

Table 2.2 Four industrial production lines involved in PV-technology based on Si

**Figure 2.5** The appearance of solar panels based on polycrystalline Si wafers and amorphous-Si thin-film materials. See also Colour Insert.

final product, it is easy to recognise the three different types of solar panels produced using crystalline Si, polycrystalline Si, and amorphous Si.

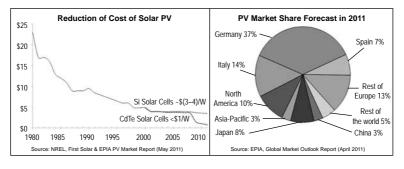

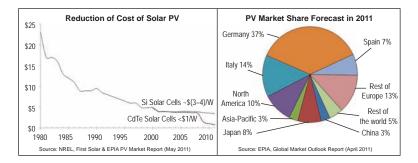

### 2.3 PV-Manufacturing Cost Based on Si Technology

The cost of PV technology is given in \$/W, as shown in the following relationship:

Cost of solar power  $\left(\frac{\$}{W}\right) = \frac{\text{Production Cost }\Downarrow}{\text{Cell Efficiency }\Uparrow}$